之前EETOP曾举办过高速电路设计分析线下培训,效果非常不错,但是线下课程价格相对较高(两天学习需要3000元)。为了让更多的人可以学习《高速电路设计分析与仿真》这门课程,我们特邀主讲老师录制了线上课程,内容与之前的线下培训基本一致。成本大大降低!现在仅需399元!

本课程基于讲师多年的实战经验,详细介绍了信号完整性(SI)、电源完整性(PI)较完整的知识体系,以及各种不同的信号完整性问题在实际项目中的体现,特别是最近DDRx技术领域,以及xGH高速信号领域的一些研究成果。通过理论和实践相结合的培养方式,帮助电子行业工程技术人员在理解高速信号传输本质的基础上,掌握分析SI问题的工具和技巧,提高PCB产品设计和不限房吗的专业技能,为企业培养优秀的SI工程师和项目管理人员,提高产品性能质量和可靠性,增强产品的市场竞争力。

本课程是使得电子系统设计工程师们在正确理解信号完整性和电源完整性的理论基础上,能够更好的掌握高速电路系统设计的方法和技巧,跟上行业发展要求。

项目经理、产品研发人员、SI工程师、测试及质量管理人员

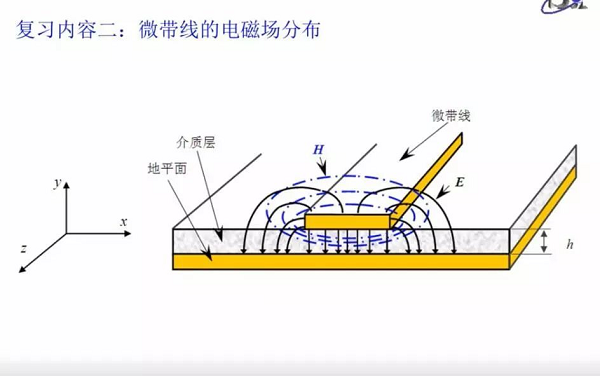

第一讲 高速系统设计与微波传输线

本课程第一讲介绍高速电路系统设计所面临的问题和挑战,然后阐述了高速信号的基本理论知识。此部分内容意在提醒读者在高速系统中遇到的新问题,以及解决这些问题所需的理论基础。本节内容着重介绍了高速信号传输的本质,以及对传输介质的要求。读者了解了高速信号传输的本质之后,能更好地理解和掌握高速设计中的关键因素和设计要求。

第二讲 SI反射分析

本节内容讲述信号完整性中的第一大类基本问题:信号的反射和分析方法。信号的反射是高速信号设计中的最基本问题之一,也是了解其他信号完整性问题的基础。本节中详细讲解了信号反射的机理,信号反射的基本计算分析方法,以及在实践中如何有效地预防和抑制反射。通过对信号反射原理和分析方法的学习,有助于读者从一开始就遵循良好的设计习惯,为安全可靠的系统设计打下一个良好的基础。

第三讲 SI串扰分析

本节内容讲述信号完整性中的第二大类基本问题:信号的串扰和分析方法。信号的串扰也是高速信号设计中的最基本问题之一,也是影响系统安全性、可靠性的关键因素。随着电子系统设计复杂性的增加,由串扰所带来的信号稳定性问题也变得更加复杂。本节中详细讲解了信号发生串扰的机理,以及在实践中如何有效地预防和抑制串扰。通过理论讲解和形象的动画演示,揭示影响串扰的各种关键因素,使读者对串扰的理解和掌握更加形象化具体化。本节中,借助对串扰的学习,还讲解了差分信号的原理和设计特点,对长期以来业界对差分信号错误的认识和设计方法给予了纠正,避免了事倍功半的盲目设计和无效设计

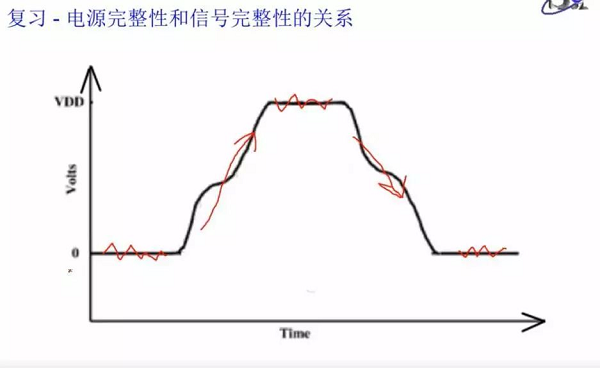

第四讲 PI分析方法

本节中,着重讲解了两个问题:电源完整性的本质,以及电源完整性和信号完整性之间的关系。尤其强调电源完整性指的是当信号处于上升沿和下降沿部分时,电源系统所发生的问题,而不是业界普遍认为的电源系统的纹波。这一错误认识,导致很多高速系统设计不得要领,走了弯路。在本节中,结合讲师自身多年的项目经验,创造性地总结了电源完整性设计的方法精髓,使读者能够直接抓住设计本质,提高设计针对性和有效性。除此之外,为使读者能够贯通理解电子产品的理念,本节还从芯片设计和系统可靠性两个角度扩充讲解电源完整性的概念,使读者重复理解电源完整性设计的必要性和局限性。

第五讲 DDR2信号完整性仿真分析实例

在学习过前面几节关于信号完整性的基本概念和设计方法之后,本节内容以DDR2的设计为例,结合工具的使用,讲述实现高速系统设计过程中,进行SI仿真分析的方法和一般流程。目的是让工程师了解该如何着手进行一个实际的高速电路的设计与分析,明确信号仿真分析所解决问题的着眼点和解决方法。如果读者能找到一个手边的实际案例,按着视频中的步骤完成设计流程,对高速信号仿真分析和设计有切身的体会,会取得更好的学习效果,完成向高速信号分析领域迈出的第一步。

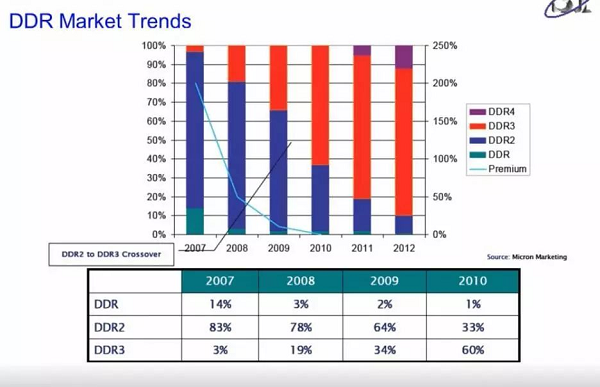

第六讲 DDRx系统设计与分析

在学习了基本的高速信号的基本问题和分析方法之后,本讲内容结合业界的实际需求,讲解DDRx存储系统技术的演变和发展。帮助读者在了解DDRx系统技术原理的基础上,理解并掌握如何设计安全高效的DDRx系统。由于DDRx系统的技术传承性,本节内容涵盖了从DDR1到DDR3的技术范围。而由于DDR4相比于前几代的DDR系统有了很多改变,在设计特点上又更多的体现在软件和硬件相结合的方式,和前几代的DDRx系统在设计方法和仿真分析技术上有所不同,因此我们将DDR4部分单独做为后续一讲。

第七讲 DDR4技术规范详解

本节针对目前主流的DDR4技术,采用和DDR3系统对比的方式,对DDR4的新增功能、关键技术和一些新方法,以及系统设计问题进行全面讲解。在充分理解和掌握DDR4的技术细节和特点后,说明问题分析思路和仿真方法。尤其是对DDR4系统启动时的初始化和校准流程的讲解,有助于读者对DDR4系统的全面掌握和理解。在目前已经实施的DDR4系统中,所出现的问题90%都和这部分内容相关。

第八讲 高速Serdes链路设计与分析第一部分

第八讲高速系统设计(第一部分),侧重于实际应用,除了讲述高速Serdes的基本原理之外,对前面几节中所讲述过的高速信号设计技术都将在这一部分进行深化讨论和理解,从理解高速信号传输的原理和本质触发,以最终的PCB设计落实为主要目的,逐一讲解和展示xGHz的高速PCB电路设计技术细节。通过这一节的学习,使读者充分理解高速信号的理论知识和实际电路设计相结合的应用技巧,知行合一,融汇贯通,为更高级的设计挑战打下坚实的基础。

第九讲 高速Serdes链路设计与分析第二部分

在本节中,第八讲高速系统设计(第二部分),侧重于xGHz信号的仿真分析。由于信号的高速率,xGHz的信号仿真分析和传统信号的仿真分析方法有很多不同,在信号的激励方式、观察角度、信号质量的评判标准,分析流程上都有所不同。通过本节的学习,读者可以了解到这些不同,以及如何做xGHz的信号仿真分析,更重要的是,这些技术都还在不断地发展完善中,因此这部分学习并不是终结,而是更好地学习和掌握更高级技术的基础。

讲师介绍

邵鹏,毕业于北京大学计算机系。历任IBM、Intel中国研究院系统架构师,研究员。从事高性能服务器基础架构研究,并负责从芯片到板级、系统全流程高速链路设计与仿真工作。